Добро пожаловать в Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

служебный телефон:86-755-83294757

Новая информация

Новая информация Первая страница

/динамика компании

/

Первая страница

/динамика компании

/

TI C54x фиксированная точка DSP - TMS320VC5409AGWS12 с тактовой частотой 20 МГц

Краткий обзор:Tms320v40409ags12 (DSP), основанный на усовершенствованной архитектуре гарварда с одной программной схемой памяти и тремя шипами пам…

Краткий обзор:

Tms320v40409ags12 (DSP), основанный на усовершенствованной архитектуре гарварда с одной программной схемой памяти и тремя шипами памяти. Процессор предоставляет высокопараллельную арифметическую логический блок (ALU), аппаратную логику для применения, память на пластинах и другие части. Основой оперативной гибкости и скорости Texas Instruments TMS320VC5409A является набор высоко специализированных команд.

Отдельные программы и пространство данных позволяют одновременно получать доступ к программам и данным, тем самым обеспечивая высокую параллельную степень. За Один цикл может выполняться две операции считывания и одна операция записи. Эта архитектура может быть использована в полной мере директивами с параллельным хранением и применением конкретных инструкций. Кроме того, данные могут быть переданы между данными и программным пространством. Эта параллельная технология поддерживает мощные арифметические, логические и битные операции, которые можно осуществить в течение одного машинного цикла. Устройство также включает механизмы управления для управления прерываниями, повторными операциями и функциональными вызовами.

Продукция: tms320vc5409ags12

Ядро: C54x

Частота: 20 МГЦ

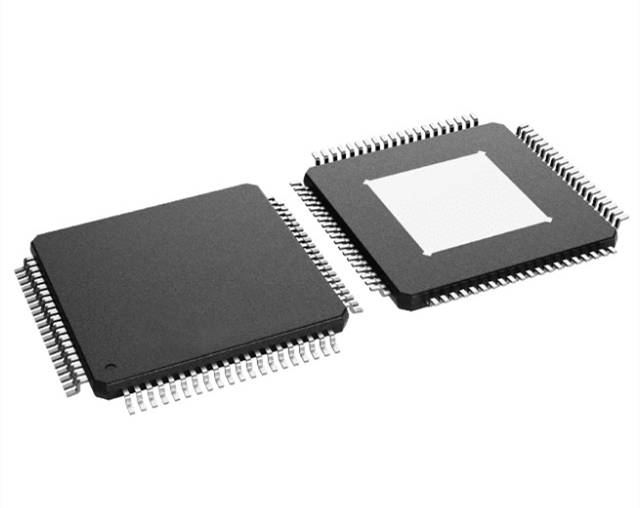

Инкапсуляция: BGA-144

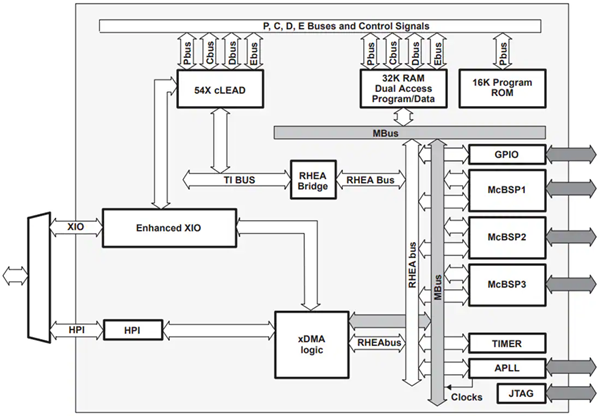

Функциональная схема:

Характеристика:

Продвинутая архитектура Multibus с тремя отдельными 16 - битными шинами памяти и одной программной памятью

40 - битная арифметическая логическая единица (ALU), включая 40 - битный перевертер в бочках и два отдельных 40 - битных сумматора

17- х х - 17- битный битный умножитель частоты, подключенный к 40 - битной специальной сети, предназначенной для однопериодических операций умножения/суммирования (мак) в непотоковых линиях

Для сравнения, отбора и хранения (CSSU), с тем чтобы добавить/сравнить варианты для операторов Viterbi

Индекс кодера используется для вычисления чисел чисел 40 - битных суммарных значений за Один цикл

2 генератора адресов, 8 вспомогательных регистров и 2 вспомогательных единицы алгоритма (ARAU).

Шина данных с функцией стента шины

Расширенные режимы адресации используются для 8M/xD7 x 16 - битного максимального адресационного внешнего программного пространства

32K на 16 битах, включая RAM

Четыре куска 8K/xD7 16 - битной программы с двойным доступом/данные RAM

Ром на 16K/xD7 x 16 битах, настроенный на программное запоминающее устройство

Усиленный внешний параллельный интерфейс (XIO2)

Одна команда повторяет и блок повторяет операции для программного кода

Блок-память-мобильная команда, реализующая лучшее программирование и управление данными

Команда с 32 - битным числом операций

Команды считываются с двумя или тремя операционными числами

Арифметические команды с параллельной хранением и параллельной нагрузкой

Команда условного запоминания

Быстрое возвращение с прерыванием

На стороне

Программируемые генераторы состояния ожидания и программируемые группы переключаются

Программируемый фазовый генератор (PLL) на скрипке, с внутренним осциллятором или внешним источником часов

16 - битный таймер

6 - канальный доступ к прямой памяти (DMA) контроллер

Три многоканальных буферных порта (McBSP)

Интерфейс HPI8/16 усиливающегося параллельного порта (hpi8/16)

Управление энергопотреблением с инструкциями IDLE1, IDLE2 и IDLE3 имеет режим потери энергии

CLKOUT отключает управление и отключает CLKOUT

Основываясь на эмуляционной логике сканирования на экране, логика сканирования границ IEEE Std 1149.1 (JTAG)

144 - й шаровой решётка (BGA).

Плоская четырехсторонняя упаковка (LQFP) (приставка PGE)

6.25 нс время выполнения монопериодической команды (160 MIPS)

Время выполнения однопериодической команды 8,33 нс (120 MIPS)

3.3V/ввода/вывода напряжения (160 и 120 MIPS)

1,6 V напряжение ядра (160 MIPS)

1.v напряжение ядра (120 MIPS)

![Поставка [Melexis] Оптические Датчики, Датчики Давления, Датчики Скорости, Датчики Температуры](/upload/202506/28/202506281122323670.jpg)

время:2025-06-28

время:2025-06-28

время:2025-06-28

время:2025-06-28

контактный телефон:86-755-83294757

предприятие QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

время службы:9:00-18:00

почтовый ящик:sales@hkmjd.com

адрес компании:КНР, Шеньчжень, Футиянь, трасса Женжонг, оф. центр «New Asia Guoli», оф. 1239-1241x

CopyRight©2021 Все права защищены Mingjiada гуандунский ICP готов к 05062024-12

официальный двухмерный код

ссылки на дружбу: