Добро пожаловать в Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

служебный телефон:86-755-83294757

Новая информация

Новая информация Первая страница

/динамика компании

/

Первая страница

/динамика компании

/

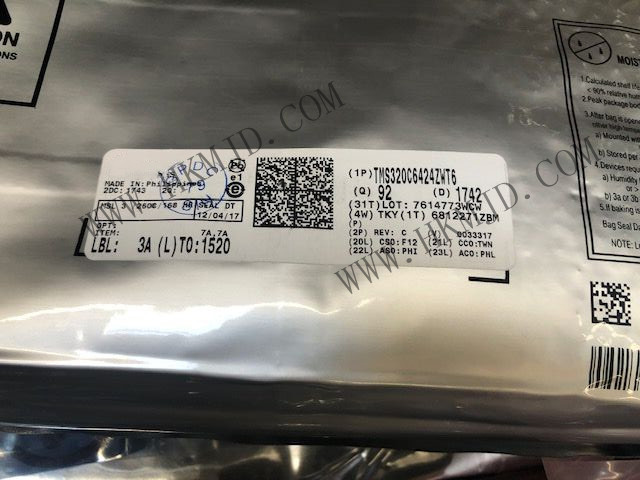

[ TI ] C64x + DSP с фиксированной точкой - TMS320C6424ZWT6 Цифровой процессор сигналов NFBGA (ZWT)

Устройство TMS320C6424ZWT6 представляет собой C64x + DSP с фиксированной точкой - до 600 МГц, 16/8-битный EMIFA, 32/16-битный DDR2, SDRAM.

Устройство TMS320C6424ZWT6 представляет собой C64x + DSP с фиксированной точкой - до 600 МГц, 16/8-битный EMIFA, 32/16-битный DDR2, SDRAM.

Инструкции:

TMS320C6424ZWT6 устройств основа на TI трет поколен высокопроизводительн старш VelociTI длин инструкц слов (VLIW) архитектур, эт TMS320C6000 ™ DSP сам высок производительн сред платформ фиксирова точк DSP продукт.

C64x+ ядро имеет производительность до 4,8 миллиардов инструкций в секунду (MIPS) при скорости 60 MHz часов, обеспечивая решение задач программирования высокой производительности DSP. Ядро DSP обладает оперативной гибкостью высокоскоростного контроллера и цифровой способностью процессора массива.

Параметры:

Ядро: C64x+

Тип: точка

Интерфейс: EBI/EMI, HPI, I2C, McASP, McBSP, UART, 10/100 ethernet MAC

Скорость: 600мгц

Память с невосприимчивостью: ром (64kB)

Пластинка RAM: 240kB

Напряжение — I/O: 1,8 V, 3,3 V

Напряжение — ядро: 1,05 V, 1,20 V

Рабоч температур: 0 ° C - 90 ° C (ти дже)

Тип установки: тип поверхностной наклейки

Инкапсуляция/оболочка: 361-LFBGA

Упаковка оборудования поставщика: 361-NFBGA (16x16)

Приложение:

телекоммуникацион

ауд

Промышленное применение

Характеристика:

Высокопроизводительный цифровой процессор (C6424)

Время командного цикла 2,5 наносекунды, 2 наносекунды, 1,67 наносекунды и 1,43 наносекунды

400, 500, 600 МГЦ C64x+ скорость часов

8 положений 32 - битной команды/цикла C64x+

3200,4000,4800,5600 MIPS

Полностью совместима с C64x

Класс бизнеса и автомобилей (Q или S)

Устройство малой мощности (суффикс L)

VLIW (VLIW)TMS 320 c 64 x+DSP ядра, разработанные компанией VelociTI

8 высоко независимых функциональных единиц с расширением velocit.2:

6 alu(32/40 бит), поддерживаемых одним 32 битом, двумя шестнадцатью или четырьмя или четырьмя битами арифметических операций на Один часовой цикл

Два мультипликатора поддерживают мультипликацию в четыре раза по 16 на 16 бит на Один тактовый цикл (результат 32 бит) или восемь умножения на 8 бит (результат 16 бит)

Загрузочная архитектура памяти с непоследовательной поддержкой

64 универсальных регистра на 32 бита

Командная упаковка сократила количество кодов

У всех команд есть условия

Другие функции улучшения C64x+

Операция защитного режима

Аномальная поддержка ошибочного обнаружения и программы

Аппаратная поддержка для автоматической фокусировки модуля на цикле модуля

Функция набора команд C64x+

Адресация байт (8/16/32/64 бит данных)

8 - разрядная защита

Извлечение, настройка, очистка поля битов

Стандартизация, насыщение, количество бит

Велоцити.2 увеличивает ортогональность

Расширение C64x+

Упорядочить 16 - битные команды

Дополнительные команды, поддерживающие множественное умножение

C64x+ L1/L2 архитектура памяти

256K бит (32K байт)L1P программа RAM/ скоростная кэшированная память (гибкое распределение)

640 килобайт (80 килобайт)L1D данных RAM/ высокоскоростной кэш (гибкое распределение)

1M бит (128K байт)L2 единое отображение оперативной/высокоскоростной кэш [гибкое распределение]

* порядок конца — поддерживает порядок малого и главного

Внешний интерфейс памяти (EMIFs)

32 - битный контроллер памяти DDR2 SDRAM с 256M байтовым адресом (1,8 V/I/O)

Поддержка шины до 333 МГЦ (скорость передачи данных) и интерфейса с DDR2-400 SDRAM

Асинхронная 16 - битная ширина эмифа (EMIFA) с адресом до 128M байт

Интерфейс на флешке

NOR(ширина 8/16 бит)

Нэнд (ширина 8/16 бит)

Увеличенный прямой доступ к памяти (эдма) контроллер (64 отдельных канала)

Два 64 - битных универсальных таймера (каждый настроен на два 32 - битных таймера)

64 - битный таймер для сторожевой собаки

Два UARTs(Один с RTs и CTS контроль трафика)

Основная/внутренняя интегральная схема (шина I2C)

Два мультиканальных буферных последовательного порта (McBSPs)

I2 и TDM

Интерфейс аудиокодека AC97

энерг

Интерфейс стандартного кодека голоса (AIC12)

Телекоммуникационный интерфейс-ST шина, H-100

Режим 128 каналов

Многоканальный звуковой последовательный порт (McASP0)

Четыре последовательных последователя и модель SPDIF (DIT)

16 - битный интерфейс главного порта (HPI)

32 бит, 33 МГЦ, 3.3V внешних компонентов (PCI)

10/100 мб/с ethernet MAC (EMAC)

Соответствует стандарту IEEE 802.3

Поддержка различных независимых интерфейсов сми (MII, RMII)

Управляемый модуль ввода/вывод данных (MDIO)

Интерфейс флинка (FPGA)

Выход модулятора тройной чакры (PWM)

Внутренняя загрузочная программа "ром"

Отдельные провинциальные модели электричества

Гибкий генератор часов PLL

Совместимый с IEEE-1149.1 (JTAG) сканирование границ

До 111 универсальных ввода/вывода (GPIO) штырей (повторно используемых с другими устройствами)

Упаковка:

361 инкапсуляция PBGA без свинца (ZWT суффикс), 0,8 мм от шара

Пластиковая упаковка BGA (ZDU суффикс), расстояние 1,0 мм

0,09 микрон /6 слоев медных металлов (CMOS)

3.3V и 1,8 V ввод/вывод, 1,2 V внутри (7/ 6/ 5/ 5/ 4/-Q6/-Q5/-Q4)

3.3V и 1,8 V ввод/вывод, 1.05V внутри (— 7/ 6/ 5/ 5/ L/ Q5)

время:2025-08-21

время:2025-08-21

время:2025-08-21

![Поставка [Micron, SK Hynix, Samsung] NAND флэш-памяти, динамической памяти с произвольным доступом](/upload/202508/21/202508211405067206.jpg)

время:2025-08-21

контактный телефон:86-755-83294757

предприятие QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

время службы:9:00-18:00

почтовый ящик:sales@hkmjd.com

адрес компании:КНР, Шеньчжень, Футиянь, трасса Женжонг, оф. центр «New Asia Guoli», оф. 1239-1241x

CopyRight©2021 Все права защищены Mingjiada гуандунский ICP готов к 05062024-12

официальный двухмерный код

ссылки на дружбу: